## IBM Systems and Technology Group

The Foundry-Packaging Partnership

**Enabling Future Performance**

Jon A. Casey

IBM Fellow IBM Systems and Technology Group

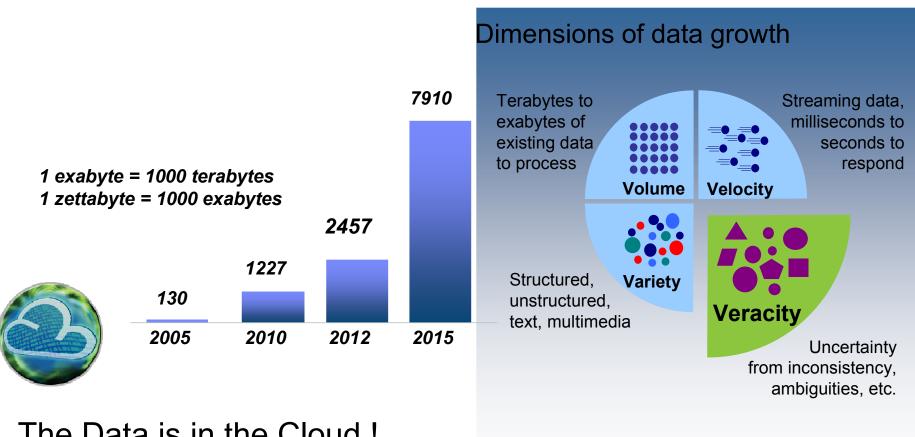

# Data growth will drive the new IT model

The Data is in the Cloud!

The Compute will move to the Da

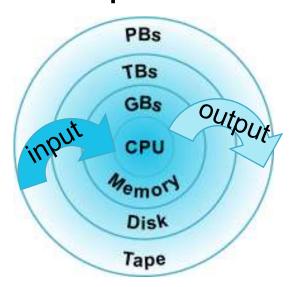

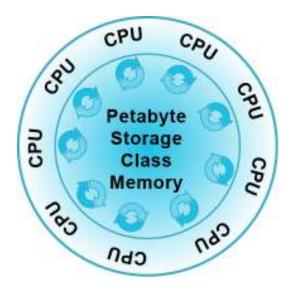

## Changes in the compute model –memory centric computing

## **Old Compute-centric Model**

Manycore FPGA

Massive Parallelism

Persistent Memory

**Phase Change**

### **New Data-centric Model**

Data lives on disk and tape Move data to CPU as needed Deep Storage Hierarchy Data lives in persistent memory Many CPU's surround and use Shallow/Flat Storage Hierarchy

Huge impact on hardware, systems software, and application design

Open Architecture, Software Defined Environment

Flash

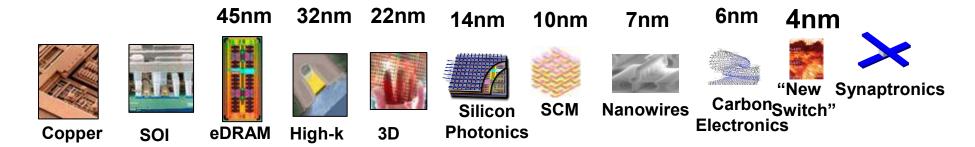

Will semiconductor technology alone get us to the goal line?

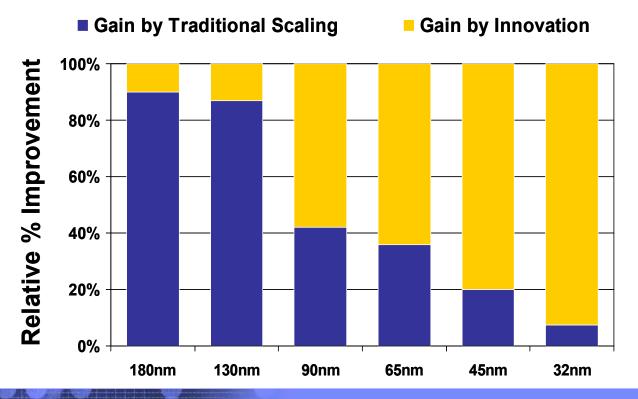

## **IBM Transistor Performance Improvement**

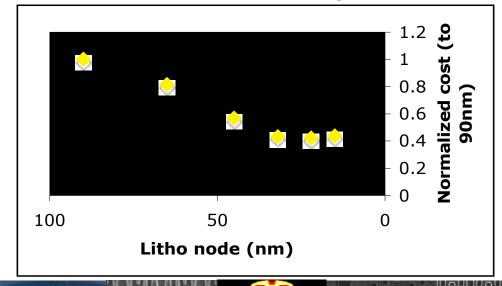

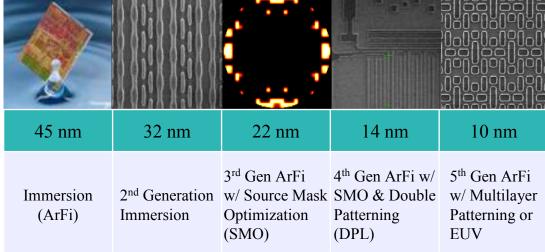

# Scaling can and will continue to at least the "7 nm" node Cost per transistor has begun to saturate

But It will be expensive

No cost-effective lithography

# Advanced packaging market trends

- Slowing of Moore's Law forces higher integration, which leads to larger die

- Systems, Networking & mobile architects are moving to higher levels of integration: 3D stacking, 2.5D interposers & MCM

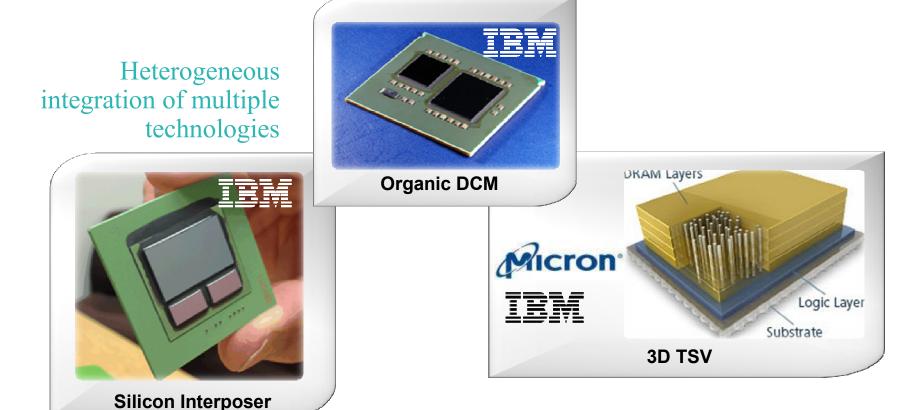

## Heterogeneous Integration and 3Di: "Volumetric Scaling"

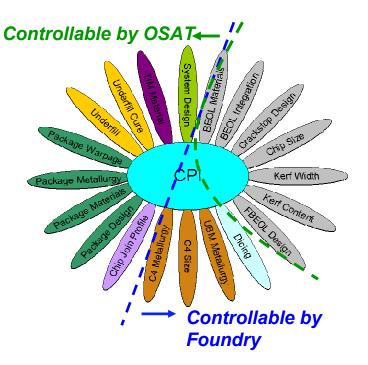

#### Requires co-development of Silicon and Packaging solutions

- Packaging is the key technology for volumetric scaling

- 2D and 3D technologies

- High performance I/O

- Optics

- CPI: Chip-Package Interaction

- Power and thermal management

#### Provides lower cost solutions to enable system performance

Si cost:performance metric is very challenged

#### Allows for use of mixed semiconductor technologies

Enables use of lower cost technologies for less performance sensitive functions

#### Currently in development at IBM

- CSP (chip scale packages)

- SIP (system in package)

- Interposers

- Si and other interposer materials

- -3Di

- Photonics

# Summary

- Silicon performance advancement becoming more challenging as scaling is becoming more costly

- Need to look beyond CMOS for cost effective technology solutions

- Integrated co-development of Silicon and Packaging solutions required to achieve new technologies with superior cost:performance metrics

- Volumetric scaling will be critical to future performance enablement

- Tightly coupled modules and components

- 3D*i* technology

- Interposer integration

- High performance I/O and optics